LED数码管动态扫描显示控制器设计

【摘要】

当多个 LED 数码管用静态方式显示时, 需要相当多的引出端线,而器件的引脚由于实际加工水平和使用需求, 往往哪个仅有极为有限的引脚数。 利用循环显示的方法, 可以通过人眼的视觉暂留, 达到使用极为有限的引脚使得多个数码管同时显示的效果。

【正文】

1. 实验任务与原理

1. 1 任务指标

采用扫描方式 LED 数码管的动态显示, 控制好数码管之间的延迟,根据视觉暂留原理对数据进行连续计数。

1. 2 功能需求

(1) 能够通过动态扫描显示数据。

1. 3 原理阐述

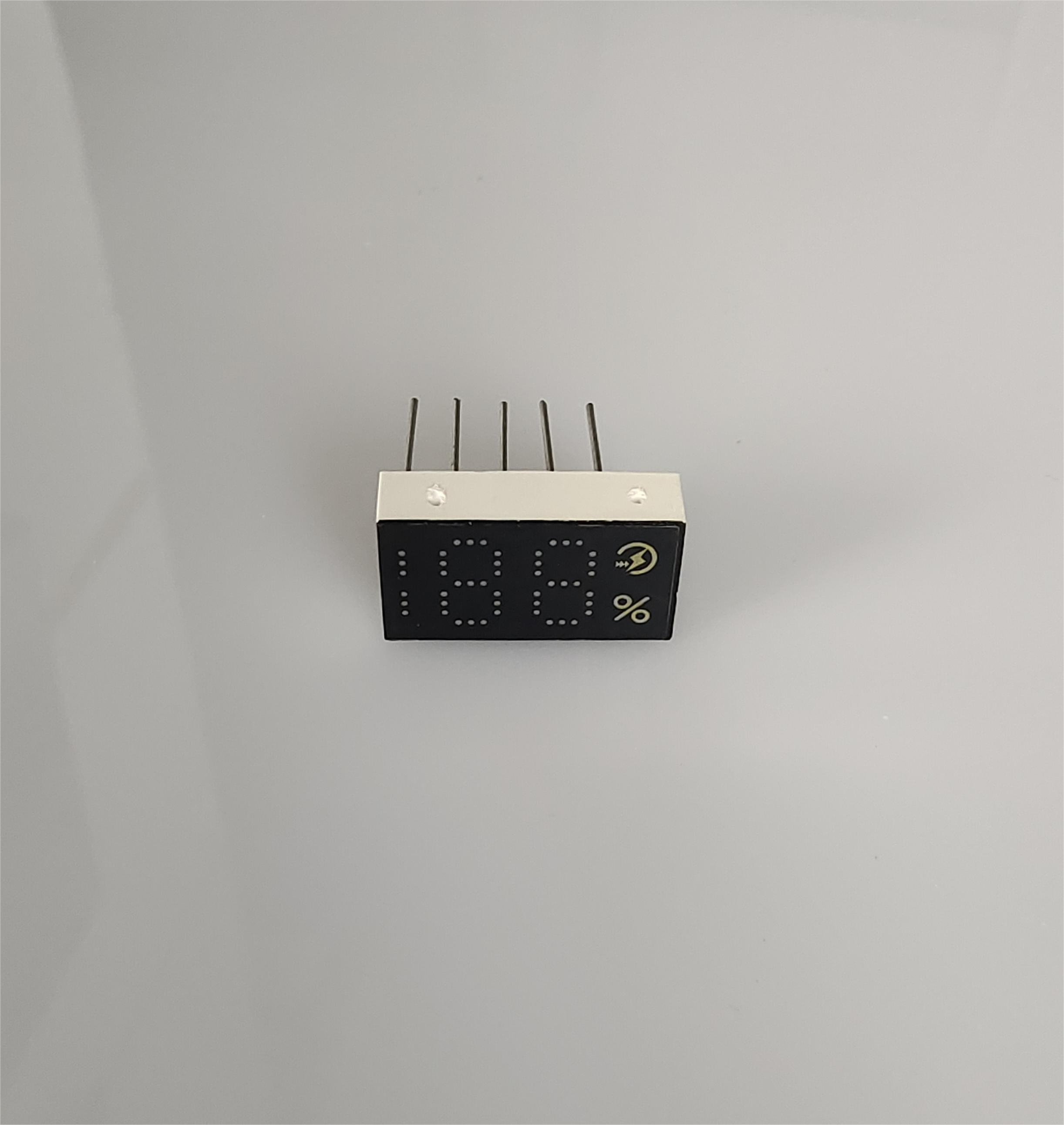

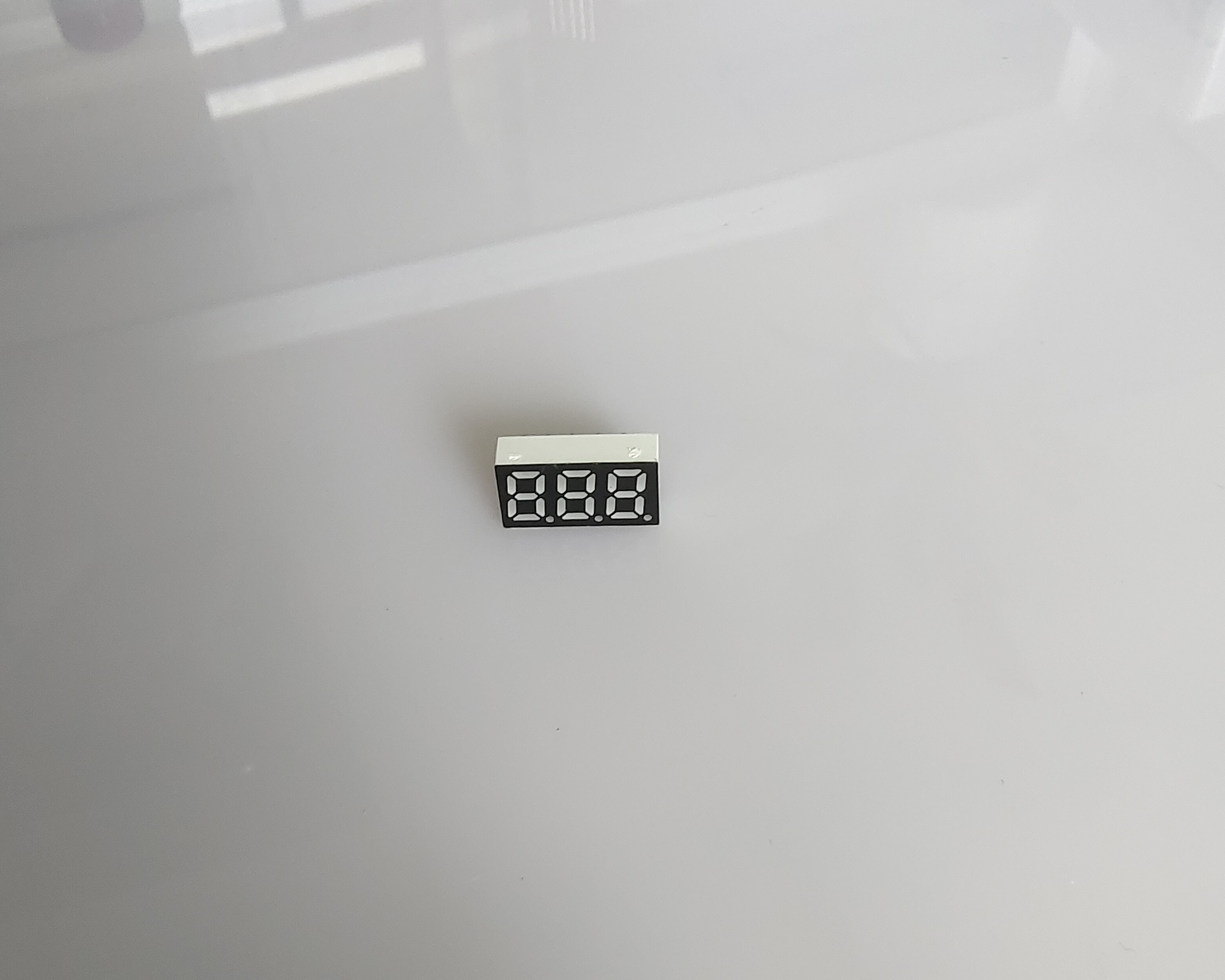

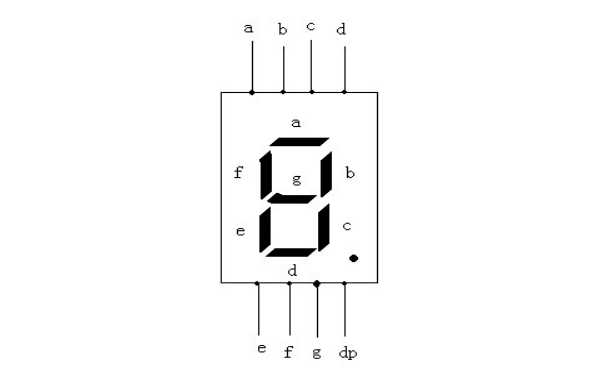

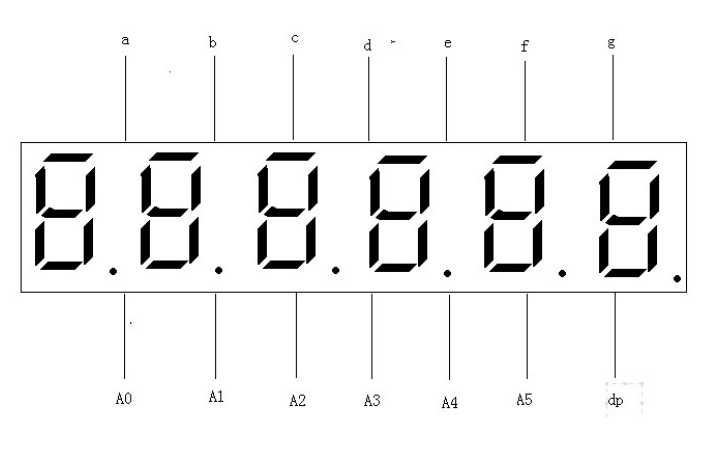

(1) LED 数码管显示原理

LED 七段数码管原理图如下, 当采用共阴极(采用共阳极时反向) 时, 共阴极接地, 另一管脚接高电平的发光二极管被点亮。

(2) 动态扫描原理

动态扫描要求在点亮多个各不同的数码管的同时输入数据,但是由于要显示多个不同的数字, 需要在多个周期内才能完成,即将时间分隔为多个周期的循环。 当频率达到一定程度时(如1khz), 其延时可达到较好的效果, 利用视觉暂留可以达到动态显示的目的。

2. 设计思路, 方法及方案

2. 1 系统功能需求分析

在时钟脉冲 clk 的作用下, 计数器开始计数, 再通过译码器生成数据选择器的片选信号, 来控制 LED 管显示。 同时选出一路 BC码数据, 通过显示译码器控制数码管 a-g 管脚和共阴极, 使得每次只有一个数码管在工作。 这样进入 clk 循环计数后, 可以在较高的频率下轮流显示。

4. FPGA 模块程序设计

4. 1 提交模块 VHDL 程序

由于程序较长, 见附录。

5. 结束语

5. 1 故障分析处理

动态扫描现实的优势是明显的, 不但减少了引脚, 增加了使用性和可操作性, 而且更加高效。 但是其难点是对频率的设置在不同的环境和需求下需要仔细选择调试。

5. 2 收获及改进意见

(1) 对 VHDL 和 modesim 有了进一步的认识。

(2) 对波形的调试仿真有了一定的经验。

(3) 了解了 VHDL 语言, 接触了初级的的硬件描述性语言。

6. 附录

---------------------------------------七段译码显示驱动电路-------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 13:35:05 07/04/2011

-- Design Name:

-- Module Name: yimaxianshi - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entityyimaxianshi is

Port ( a : in STD_LOGIC_VECTOR (3 downto 0);

led7s : out STD_LOGIC_VECTOR (7 downto 0));

endyimaxianshi;

architecture Behavioral of yimaxianshi is

begin

process(a)

begin

case a is

when "0000"=>led7s<="01111110";

when "0001"=>led7s<="00110000";

when "0010"=>led7s<="01101101";

when "0011"=>led7s<="01111001";

when "0100"=>led7s<="00110011";

when "0101"=>led7s<="01011011";

when "0110"=>led7s<="01011111";

when "0111"=>led7s<="01110000";

when "1000"=>led7s<="01111111";

when "1001"=>led7s<="01111011";

when others=>led7s<="00000000";

end case;

end process;

end Behavioral;

---------------------------------------------count6-------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 13:49:48 07/04/2011

-- Design Name:

-- Module Name: count6 - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity count6 is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

en : in STD_LOGIC;

q : out STD_LOGIC_VECTOR (2 downto 0);

co : out STD_LOGIC);

end count6;

architecture Behavioral of count6 is

signalcq:std_logic_vector(2 downto 0);

begin

process(clk,rst,en)

begin

if(rst='0')then

cq<="000";

elsif(clk'event and clk='1')then

if(en='1')then

if(cq="101")then

cq<="000";

elsecq<=cq+1;

end if;

end if;

end if;

q<=cq;

end process;

process(clk)

begin

if(clk'event and clk='1')then

if(cq="101")then

co<='1';

else co<='0';

end if;

end if;

end process;

end Behavioral;

----------------------------------------decode38------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 13:58:13 07/04/2011

-- Design Name:

-- Module Name: decode38 - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity decode38 is

Port ( a : in STD_LOGIC_VECTOR (2 downto 0);

y : out STD_LOGIC_VECTOR (5 downto 0));

end decode38;

architecture Behavioral of decode38 is

begin

process(a)

begin

case a is

when"000"=>y<="000001";

when"001"=>y<="000010";

when"010"=>y<="000100";

when"011"=>y<="001000";

when"100"=>y<="010000";

when"101"=>y<="100000";

when others=>y<="000000";

end case;

end process;

end Behavioral;

--------------------------------------数据选择器--------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 13:49:48 07/04/2011

-- Design Name:

-- Module Name: count6 - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity count6 is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

en : in STD_LOGIC;

q : out STD_LOGIC_VECTOR (2 downto 0);

co : out STD_LOGIC);

end count6;

architecture Behavioral of count6 is

signalcq:std_logic_vector(2 downto 0);

begin

process(clk,rst,en)

begin

if(rst='0')then

cq<="000";

elsif(clk'event and clk='1')then

if(en='1')then

if(cq="101")then

cq<="000";

elsecq<=cq+1;

end if;

end if;

end if;

q<=cq;

end process;

process(clk)

begin

if(clk'event and clk='1')then

if(cq="101")then

co<='1';

else co<='0';

end if;

end if;

end process;

end Behavioral;

同类文章排行

- LED数码管的检测

- LED数码管故障检测检修

- LED数显温度控制器设计论述

- LED大屏幕数显装置在随流孕育装置上的应用

- LED数码管正装与倒装结构区别

- led数码管静态显示方式和动态显示方式

- LED七段数码管数字钟

- led数码管显示种类简介

- LED数码管显示器介绍

- LED数码管动态扫描显示控制器设计